AMD EPYC Bergamo, svelata l’architettura alla base dei chip enterprise, con un’efficienza e una densità dei core senza precedenti grazie a Zen 4C.

Grazie a una serie di diapositive rilasciate da TechPowerUp, AMD ha svelato nuove e interessanti informazioni sulla sua architettura Zen 4C, il cuore dei nuovi chip enterprise EPYC Bergamo. Le diapositive rivelano tre varianti dei chip EPYC: l’EPYC 9654, già noto al pubblico, l’EPYC 9684X con CPU Genoa-X, incentrato su una maggiore cache per core, e infine l’EPYC 9754 con CPU Bergamo, progettato per ottimizzare l’efficienza e la densità dei core grazie all’architettura Zen 4C.

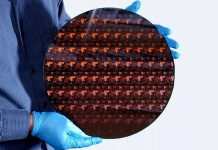

AMD ha dettagliato come ogni core Zen 4C delle CPU Bergamo avrà un’area di soli 2,48 millimetri quadrati, inclusa la cache L2, a confronto con i 3,84 millimetri quadrati dei core Zen 4 standard. Nonostante la differenza di dimensioni, entrambi i tipi di core vengono realizzati attraverso il processo produttivo a 5 nm di TSMC.

Questo significa che AMD è riuscita a raddoppiare il numero di core, mantenendo la stessa quantità di cache L2, in un die solo leggermente più grande (circa il 10%) rispetto a Zen 4. Ogni componente del CCD (Core Complex Die) di Zen 4C, denominato Dionysus, è stato ridotto da un 35% a un 45%. Nel complesso, ogni pacchetto Bergamo contiene ben 82 miliardi di transistor.

Tuttavia, AMD EPYC Bergamo ha dovuto fare un piccolo compromesso sulla cache di terzo livello, che è stata ridotta da 4 MB a 2 MB. Al di là di questo, tutte le altre specifiche tecniche rimangono invariate. Ogni die contiene 16 core Zen 4C, pertanto un chip Bergamo completo si compone di 128 core suddivisi su 8 CCD, con un totale di 256 MB di cache di secondo livello. Il Thermal Design Power (TDP) può raggiungere i 400 W, a seconda del modello specifico, e utilizza lo stesso socket SP5 degli altri chip EPYC di quarta generazione.

Le specifiche della piattaforma includono un supporto fino a 12 canali per la memoria RAM DDR5 ECC, con velocità fino a 4800 MT/s e capacità fino a 12 TB nei sistemi dual-socket. Inoltre, offre 160 linee PCIe Gen 5, 12 linee PCIe Gen 3, 32 linee SATA, e 64 linee CXL 1.1+. Le funzionalità di sicurezza integrano Secure Boot, SME, SEV-ES, SEV-SNP.

AMD ha già iniziato a spedire i primi chip EPYC Bergamo ai clienti, e prevede che la produzione raggiungerà la piena capacità entro la fine di quest’anno. Queste innovazioni testimoniano l’impegno di AMD nel ridefinire i limiti delle prestazioni dei chip per data center, promettendo un futuro più efficiente e potente per l’enterprise.